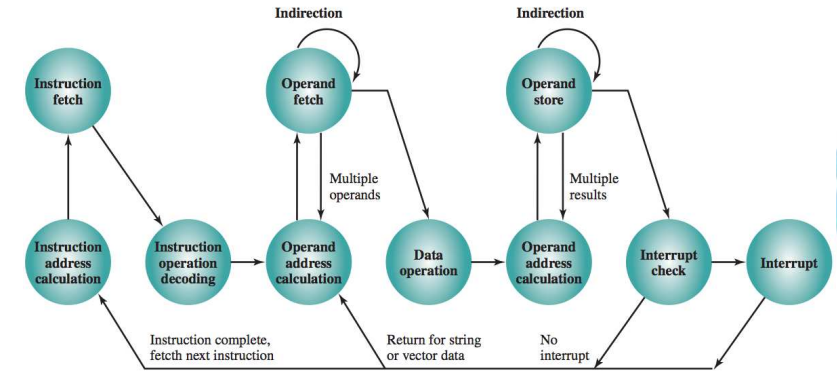

In this stage, the processor retrieves the instruction from memory. The memory address of the

instruction is usually stored in a Program Counter (PC), which is a register that keeps

track of the address of the next instruction to be executed.

In this stage, the processor decodes the fetched instruction to determine what action needs to be performed. This involves interpreting the opcode (operation code) and identifying the operands or data required for execution.

This is the stage where the actual operation specified by the decoded instruction takes place. Depending on the type of instruction, this can involve arithmetic operations, logical operations, data movement between registers, or branch operations.

For instructions that involve reading from or writing to memory (e.g., LOAD, STORE), a memory access stage is necessary.

In some cases, the results of the executed instruction need to be written back to a register or memory. For example, if an arithmetic operation results in a new value, that value must be written back to a register.