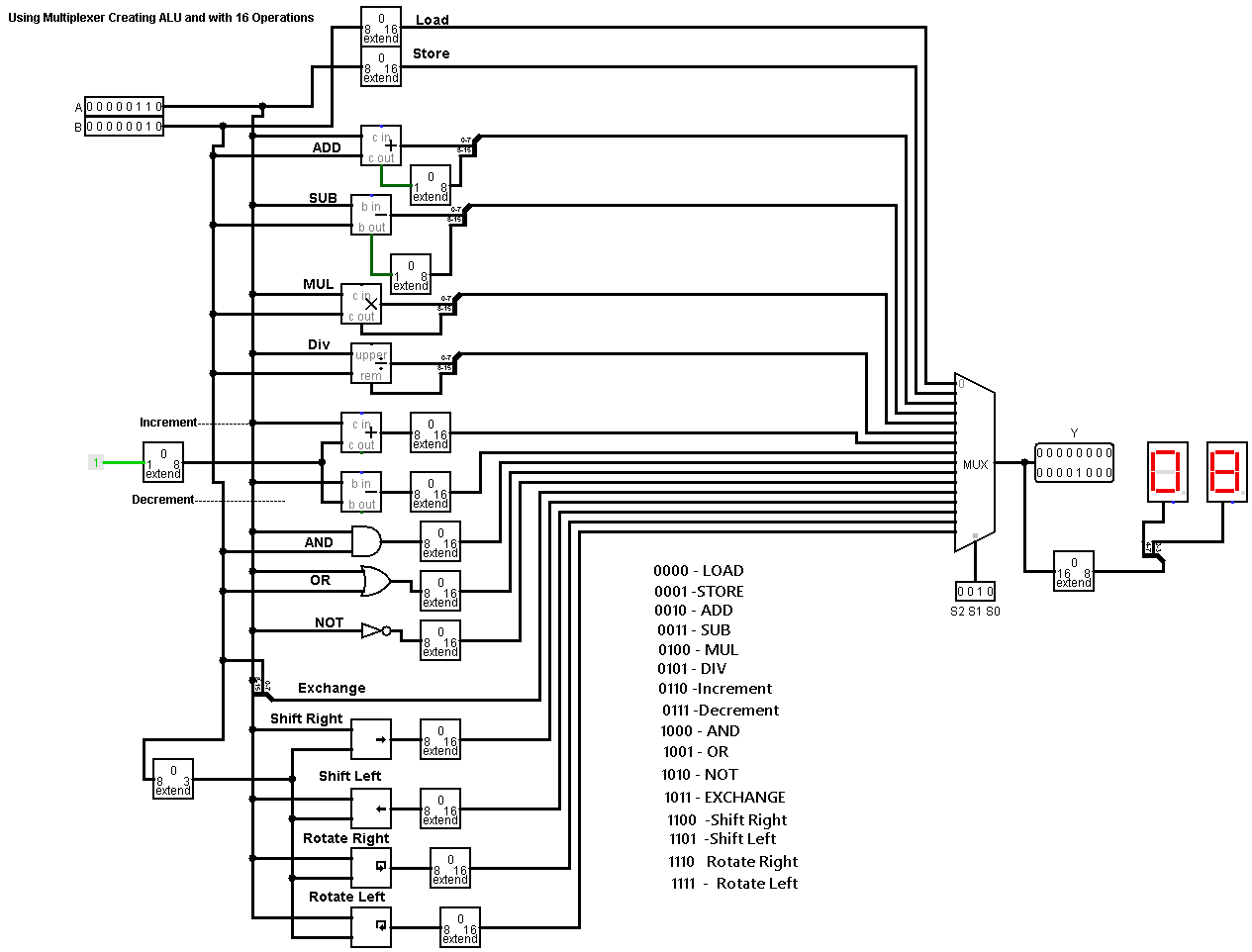

An 8-bit ALU is like a mini math genius inside a computer chip that works with 8-bit numbers. These numbers are sequences of 8 zeros and ones, meaning it can handle values ranging from 0 to 255. The ALU is really skilled at math and logical operations, such as:

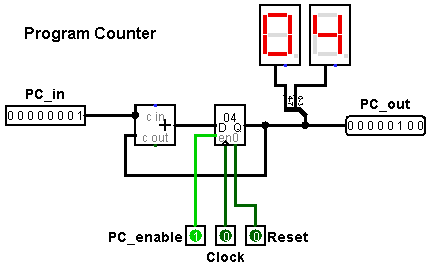

The Program Counter (PC) is a vital register in a computer's processor, overseeing the memory address of the upcoming instruction and guiding the sequential execution of a program.

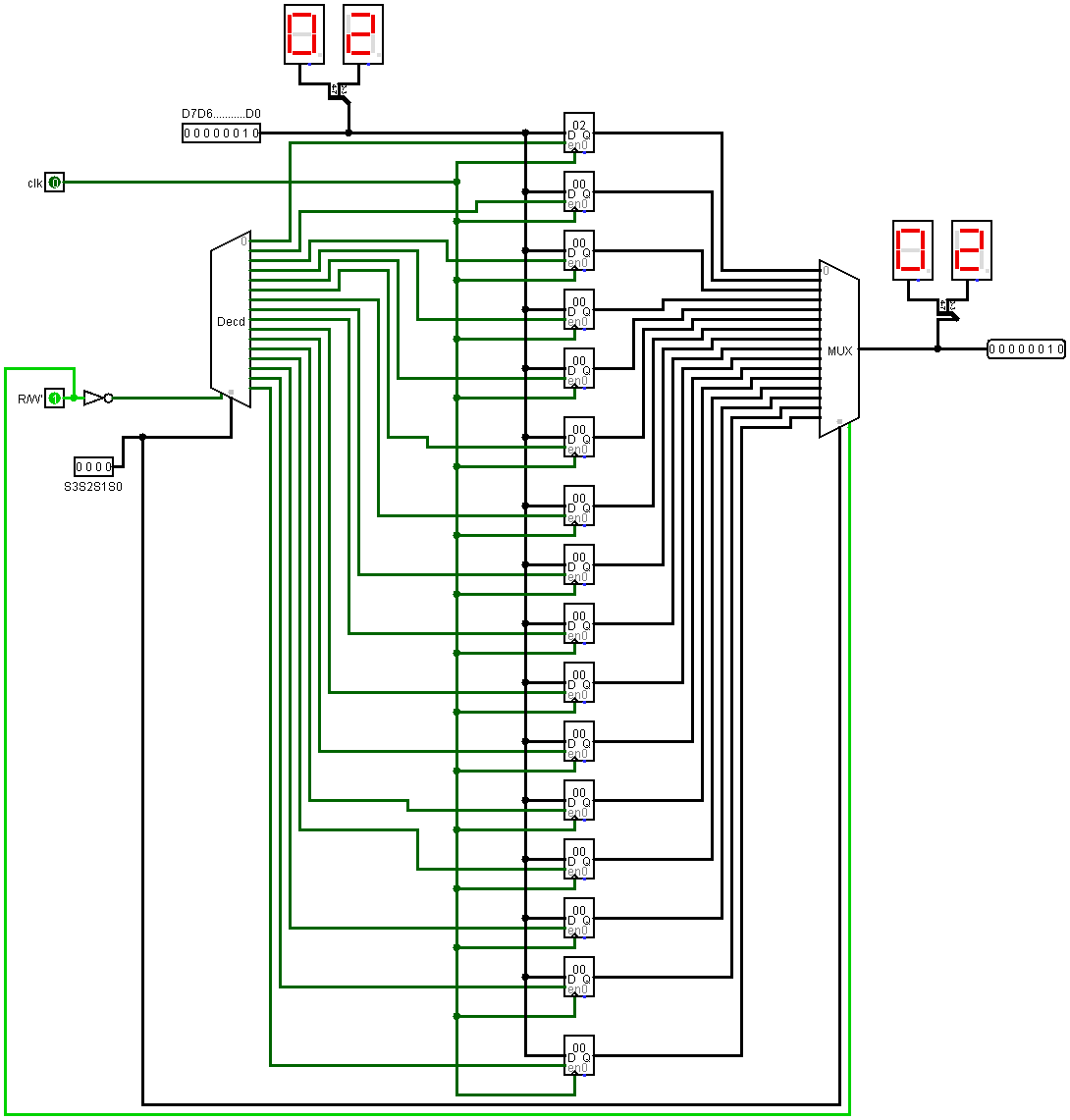

The register file in an 8-bit processor is a collection of 16 general-purpose registers, each capable of storing 8-bit data. These registers serve as small, high-speed storage units that the CPU can quickly access during processing tasks, enabling efficient execution of instructions and temporary data storage.

The register file in an 8-bit processor consists of 16 general-purpose registers (R0 to R15), each capable of storing 8-bit data. These registers are selected using a 4-bit binary address :

When a specific register is selected (e.g., R0 with address 0000), the processor can write 8-bit data into that register. The write operation is triggered by a control signal, allowing the data to be stored in the selected register.

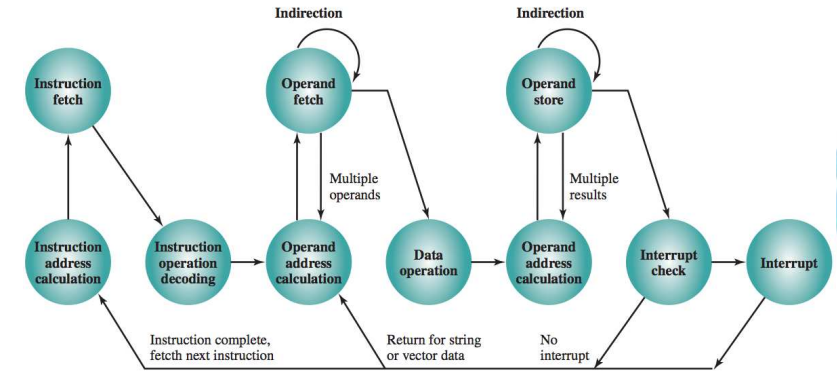

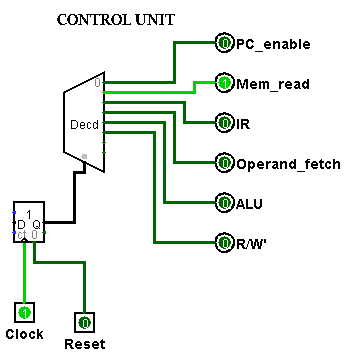

The Control Unit (CU) is a fundamental part of a computer's processor that acts as the central command center for coordinating all operations. Its primary function is to direct the flow of data and instructions within the processor, ensuring that tasks are executed in the correct sequence and at the right time.

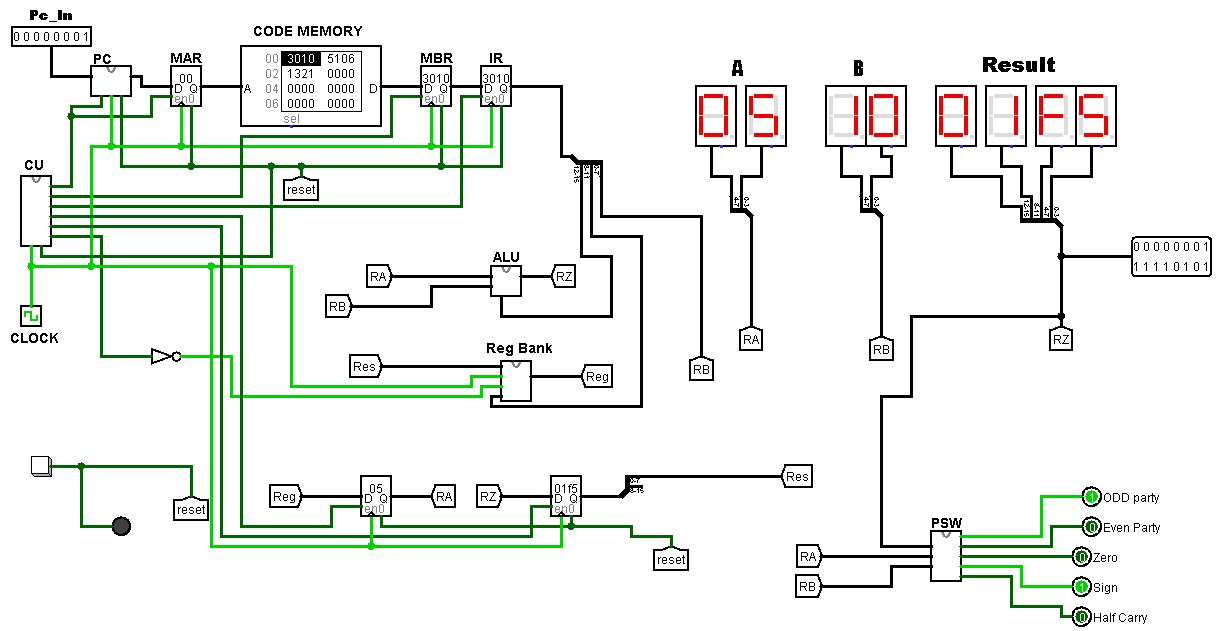

This diagram represents the architecture of an 8-bit processor using a 2-address format for immediate addressing mode, where instructions involve operations between a constant value (immediate data) and a register. Here's an explanation of how this processor operates:

Program Counter (PC): Holds the address of the next instruction to execute. It increments automatically unless a jump or branch modifies it.

Memory Address Register (MAR): Receives the address from the PC and sends it to memory to fetch instructions or data.

Memory Buffer Register (MBR): Temporarily holds fetched data or instructions from memory.

Instruction Register (IR): Stores the current instruction for decoding and execution.

Control Unit (CU): Decodes the instruction and generates control signals for execution. It orchestrates operations like PC enable, memory read, instruction fetch, and operand fetch.

Register Bank: Contains general-purpose registers (e.g., RA, RB) to store operands and results. RZ is used for storing ALU results.

Arithmetic Logic Unit (ALU): Performs arithmetic (e.g., addition, subtraction) and logical operations (e.g., AND, OR, XOR). It takes inputs from the register bank and stores results in RZ.

Clock: Synchronizes all operations and ensures sequential execution of instructions.

Example Execution: If the instruction is ADD RA, #05, the processor will: